# Automation Techniques in C++ Reverse Engineering

Rolf Rolles, Möbius Strip Reverse Engineering

August 5, 2019

### Dynamic Structure Reconstruction

Existing DBI-Based Approaches Limitations of DBI-Based Solutions My Contributions to this Problem

### Dynamic Resolution of Argument Types

Preprocessing

Run-Time Data Collection

Applying the Results

### Further Extensions and Challenges

Extensions Challenges

#### Conclusion

#### Genesis of this Research

- ▶ While researching an upcoming C++ RE training class, I:

- Practiced statically reverse engineering large C++ binaries.

- ► Spent ~85%-95% of my time creating and setting types.

- Experimented with automating type-related activities.

- A few of my results are detailed in this presentation.

- ▶ Goal: derive type-related metadata from runtime allocation and structure access data, and apply it in IDA and Hex-Rays.

- The techniques are simple, but the results are very useful!

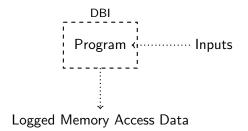

- Two primary analyses, both based on DLL injection:

- Track structure accesses

- 2. Track data flow from allocation sites into function arguments

#### Type Information

```

__int64 __fastcall sub_17142D60(__int64 a1, _DWORD *a2)

unsigned int8 *v3; // rbp

int64 v4; // rsi

int64 result; // rax

if ( a2 != ( DWORD *) a1 )

v3 = (unsigned int8 *)(a2 + 8);

v4 = a1 + 32;

if (a2 + 8 != (DWORD *)(a1 + 32))

sub 17144EB0((unsigned int8 *)(a1 + 32));

sub 17142E10(v4, v3);

if ( a2 + 12 != ( DWORD *)(a1 + 48) )

sub 17144EB0((unsigned int8 *)(a1 + 48));

sub 17142E10(a1 + 48, (unsigned int8 *)a2 + 48);

if ( a2 + 16 != ( DWORD *) (a1 + 64) )

sub 17144EB0((unsigned int8 *)(a1 + 64));

sub 17142E10(a1 + 64, (unsigned int8 *)a2 + 64);

*( DWORD *) (a1 + 24) = a2[6];

*( DWORD *) a1 = *a2;

result = (unsigned int)a2[1];

*( DWORD *)(a1 + 4) = result;

return result;

```

Type information is the difference between this: unreadable, borderline useless gibberish . . .

#### Type Information

```

void fastcall sub 17142D60(minsn_t *a1, minsn_t *a2)

mop t *v3; // rbp

mop t *v4; // rsi

if ( a2 != a1 )

v3 = &a2->1:

v4 = &a1->1;

if ( &a2->1 != &a1->1 )

sub 17144EB0 (&a1->1);

sub 17142E10 (v4, v3);

if ( &a2->r != &a1->r )

sub 17144EB0 (&a1->r);

sub 17142E10(&a1->r, &a2->r);

if ( &a2->d != &a1->d )

sub 17144EB0 (&a1->d);

sub 17142E10(&a1->d, &a2->d);

a1->ea = a2->ea:

a1->opcode = a2->opcode;

a1->iprops = a2->iprops;

```

... and this: nearly perfect code versus the original source, minus names and comments. However, it is tedious to create and apply type information, so let's automate it.

Interesting Type-Related Information

Discover, through dynamically executing the program:

- All exercised allocation sites and their sizes

- Size and layout of structures; sizes for its fields

- Also discover structures contained within other structures

- All locations accessing allocated structures of interest

- Type relationships between fields of different structures

- Function argument and local variable types

(And, some more experimental stuff described later.)

Numbers for my Current Target

These techniques allowed me to automatically (or semi-auto.) create and apply type information for my current target:

| Structures recovered       | ~200    |

|----------------------------|---------|

| Structure references added | 10,000+ |

| Union selections applied   | ~2,200  |

| Variable types modified    | ~6,000  |

| Argument types modified    | ~2,750  |

|                            |         |

Existing DBI-Based Approaches

Locate Memory Management Functions Hook Memory Management Functions Run the Program, Instrumented Instrument Memory References Detect and Record Structure Accesses Post-Process Recorded Data

Limitations of DBI-Based Solutions

My Contributions to this Problem

#### Inspiration

- Existing academic work on the subject inspired me:

- ► Howard: A Dynamic Excavator for Reverse Engineering Data Structures by Slowinska et al

- dynStruct: An Automatic Reverse Engineering Tool for Structure Recovery and Memory Use Analysis by Mercier

- ▶ The author has published the source code on GitHub.

- I adapted and modified their ideas for better performance and increased flexibility.

- For example, I use DLL injection instead of DBI.

#### Overview

The workflow of these tools is as follows:

- 1. Locate addresses of malloc, free, etc.

- 2. Hook these memory routines at runtime to record:

- ► The allocation site (e.g., address of the call to malloc)

- ► The size of the allocation

- The pointer returned by malloc

- Discard this information upon a call to free

- 3. Run the program under dynamic binary instrumentation (DBI).

- 4. Instrument every instruction that accesses memory.

- 5. Upon memory access, if address is within an allocation, log:

- Address of referencing instruction

- Allocation details (allocation site and size)

- Accessed offset within allocation

- 6. Post-process the data to build higher-level information.

Step #1: Locate Memory Management Functions

```

free proc near push ebp mov ebp, esp ...

.idata:61EB19CC extrn _imp_malloc:dword malloc proc near push ebp mov ebp, esp ...

```

Locate and record pointers to memory management functions.

(Of course, these may be contained in the binary and require direct hooks.)

This step is not specific to DBI.

Step #2: Hook Memory Management Functions

```

.idata:61EB19C8 extrn __imp_free:dword ______ &freeHook

.idata:61EB19CC extrn __imp_malloc:dword ______ &mallocHook

HOOK

```

Hook the routines, point them to our wrappers around them (somewhere inside of the same address space).

This step is not specific to DBI.

Skeletons for the Memory Management Wrappers

The hooks save metadata upon malloc, and discard upon free.

```

void *mallocHook(int size) {

#1 void *mem = pfnOriginalMalloc(size);

#2 remember(mem,size,_ReturnAddress());

#3 return mem;

}

```

- 1. Invoke the original malloc

- 2. Record the pointer / size / allocation site

- 3. Return the allocated pointer

```

void freeHook(void *mem) {

#1 forget(mem);

#2 pfnOriginalFree(mem);

}

```

- 1. Remove metadata about that allocation

- 2. free it

This works transparently to unmodified applications.

remember and Allocation Records

#### remember stores allocation records.

#### Allocation Record

| Allocated pointer | Size | RVA of return address from malloc |

|-------------------|------|-----------------------------------|

|                   |      |                                   |

The allocation site is written as an RVA (offset into image).

```

.text:61EC53EE call malloc

.text:61EC53F3 mov rbx, rax ◀

```

Base address is 61EB0000, so RVA  $\triangleleft$  = 61EC53F3-61EB0000 = 153F3.

Implementation of remember and forget

remember stores pointers and metadata in a tree (map) structure.

forget removes items from the tree.

Data should be kept sorted so we can lookup addresses within allocations. Binary trees (AVL, red/black) are well-suited; hash tables generally aren't.

### Existing DBI-Based Approaches

Locate Memory Management Functions Hook Memory Management Functions

### Run the Program, Instrumented

Instrument Memory References

Detect and Record Structure Accesses

Post Process Recorded Data

Step #3: Run Program under Instrumentation

Run the program under dynamic binary instrumentation. Provide inputs that exercise as much functionality as possible.

.text:61F33E6A call sub 61F33950

Step #4: Instrument Memory References

```

.text:61F33E5A mov eax, [ebp+4]

.text:61F33E60 add edx, 4

.text:61F33E63 mov ebx, [eax+8]

.text:61F33E69 push ebx

callbac

every

```

Insert DBI memory access callback routine before **every** memory access

Use DBI to instrument **every** memory reference.

Step #5: Detect, Record Structure Accesses

- Lookup accessed addresses in the map. <</p>

- ▶ If the access was within an allocation, log the details. ◀

- Next slide gives an example.

Step #5: Detect, Record Structure Accesses

Suppose this instruction accesses address DC07928:

.text:61F33E63 mov ebx, [eax+8]

Suppose further that we have recorded this allocation record:

We found an access! Log the following data:

| Allocation RVA  | 6F00B |

|-----------------|-------|

| Allocation Size | 80    |

| Instruction RVA | 83E63 |

| Access Size     | dword |

| Access Offset   | 0×28  |

| Access Type     | READ  |

### Existing DBI-Based Approaches

Locate Memory Management Functions Hook Memory Management Functions Run the Program, Instrumented Instrument Memory References Detect and Record Structure Accesses Post-Process Recorded Data

Step #6: Post-Process Recorded Data

So far, we have logged access data to allocated objects, as in:

| Allocation |      | Inst.  | Access |      |       |

|------------|------|--------|--------|------|-------|

| RVA        | Size | RVA    | Offset | Size | Туре  |

| 6F00B      | 50   | 6D04A  | 0×48   | 4    | WRITE |

| 14F40C     | 50   | 6B84D  | 0×18   | 4    | READ  |

| 14C213     | 50   | 6B859  | 0×4    | 4    | READ  |

| 55816      | 50   | 1E0E4  | 0×44   | 4    | READ  |

| E941A      | 50   | BD7DC  | 0×10   | 8    | WRITE |

| 6F00B      | 50   | 6D000  | 0×8    | 8    | READ  |

| 55816      | 50   | 6D00B  | 0×0    | 4    | WRITE |

| 6F00B      | 50   | 149E8D | 0×20   | 1    | READ  |

Now we process this data to reconstruct useful information.

This step is not specific to DBI.

Segregate Data by Allocation Site

|          | Allocation |      | Inst.  | Access |      | ;     |

|----------|------------|------|--------|--------|------|-------|

|          | RVA        | Size | RVA    | Offset | Size | Туре  |

| <b>•</b> | 6F00B      | 50   | 6D04A  | 0×48   | 4    | WRITE |

|          | 14F40C     | 50   | 6B84D  | 0×18   | 4    | READ  |

|          | 14C213     | 50   | 6B859  | 0×4    | 4    | READ  |

|          | 55816      | 50   | 1E0E4  | 0×44   | 4    | READ  |

|          | E941A      | 50   | BD7DC  | 0×10   | 8    | WRITE |

|          | 6F00B      | 50   | 6D000  | 0×8    | 8    | READ  |

|          | 55816      | 50   | 6D00B  | 0×0    | 4    | WRITE |

|          | 6F00B      | 50   | 149E8D | 0×20   | 1    | READ  |

First, group accesses by their allocation site.

(If two sites are known to allocate the same type, we can merge their data.)

Rebuild C-Level Structures

For a given allocation site:

| Offset | Size |           |

|--------|------|-----------|

| 0×0    | 4    |           |

| 0×4    | 4    |           |

| 0×8    | 8    |           |

| 0×10   | 8    |           |

| 0×18   | 4    |           |

| 0×20   | 1    |           |

| 0×21   | 1    |           |

| 0×22   | 2    |           |

|        | ٠.   | <b>'.</b> |

1. Sort accesses, remove duplicates.

Rebuild C-Level Structures

For a given allocation site:

| Offset | Size | struct X { |  |

|--------|------|------------|--|

| 0×0    | 4    | int f0;    |  |

| 0×4    | 4    | int f4;    |  |

| 0×8    | 8    | int64 f8;  |  |

| 0×10   | 8    | int64 f10; |  |

| 0×18   | 4    | int f18;   |  |

| 0×20   | 1    | char f20;  |  |

| 0×21   | 1    | char f21;  |  |

| 0×22   | 2    | short f22; |  |

|        |      |            |  |

- 1. Sort accesses, remove duplicates.

- 2. Create properly sized and padded fields. (Easy, right? ...)

#### Discover Nested Subobjects

Brief digression: discovery of nested structure locations.

| mov ebx, [ea    | ax+▶8 <b>∢</b> ] |

|-----------------|------------------|

| Allocation RVA  | 6F00B            |

| Allocation Size | 80               |

| Access Offset   | ▶ 0x28 ◀         |

- ▶ Notice that the instruction vs. accessed offsets are different:

- ► The instruction uses offset ►8◀; however:

- The logged, raw offset into the allocation was ▶ 0x28 ◄.

- ► Hence, when logged, eax pointed +0x20 into the allocation.

- ► Usually, this implies a structure is contained at offset +0x20.

- The alternative is a pointer to a contained POD type field.

- ▶ We can use this information to recover nesting relationships.

- Reconstruct not just a flat list of fields, but contained structs.

Sources of Ambiguity in the Data

Imperfect data (misleading, conflicting, or hard-to-analyze structure field accesses) arises from:

- Natural causes in the source code.

- Casts between integer sizes

- Use of unions

- Arrays

- Compiler optimizations.

- Bulk data operations.

A summary of these problems and our solutions follow.

Ambiguity #1: Casting

- Casts produce different access sizes to the same field.

- ▶ My solution: choose the most frequently-occurring size.

- Works well in this case.

Ambiguity #2: Compiler Optimizations

if(x->flags32 & 0x40) might compile to:

```

F7 06 40 00 00 00 test dword ptr [esi], 40h

OR, EQUIVALENTLY:

F6 06 40 test byte ptr [esi], 40h

```

- Peephole optimizers may produce the smaller, second one.

- ▶ This can produce different access sizes to the same fields.

- My solution: same as before. Also works well.

Ambiguity #3: Compiler Optimizations and Phantom Fields

if  $(x\rightarrow flags 32 \& 0x400 \bigstar)$  might compile to:

```

test dword ptr [esi], 400h ★

OR, EQUIVALENTLY:

test byte ptr [esi+1], 4h •

```

- ▶ Similar to before, but the access location increments by 1.

- Notice the different constants 400h ★ vs. 4h •.

- ▶ This can produce phantom fields within the structure.

- My solution: same as before. Also works well.

Ambiguity #4: Store Aggregation

- ► Compiler may merge adjacent writes < into a larger write.

- ▶ Produces accesses bigger than the field in question.

- My solution: choose the most frequently-occurring size.

- Works well in this case.

Ambiguity #5: Bulk Copies and Assignments

```

memset(x1,0,sizeof(X)) might compile to:

struct X {

char a;

xor

eax, eax

char b:

qword ptr [rcx], rax ◀

mov

short c;

qword ptr [rcx+8], rax

mov

int d:

qword ptr [rcx+10h], rax

mov

// ...

qword ptr [rcx+18h], rax

mov

```

- ► Compiled memset and memcpy often use block operations, i.e., are oblivious to the sizes/configurations of structure fields.

- ▶ This can produce different access sizes to the same fields.

- My solution: same as before. Also works well.

Ambiguity #6: unions

```

struct X {

// ...

union {

int a;

char *b;

}

// ...

char *b;

}

char *b;

mov eax, [rsi+10h]

}

// ...

char *d = x->b;

... might compile to ...

mov rax, [rsi+10h]

```

- ► With unions, multiple variables (of different types and sizes) occupy a single memory location.

- ▶ Clearly there can be multiple sizes for one location.

- My solution: as before, choose the most frequent size.

- ► That is, sidestep and ignore unions completely.

- Not a real solution, and does not work very well!

Ambiguity #7: Array Accesses

- Arrays produce references to non-constant offsets.

- ▶ My solution: discard accesses with non-constant offsets.

- Also not a real solution.

- Does not recover arrays, period, let alone do it well.

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

My Contributions to this Problem

### Limitations of DBI-Based Solutions

Limitation #1: Overhead from Instrumentation

- ▶ The technique is comprehensive and fully automated, but . . .

- **Every** memory access must be instrumented.

- **Every** memory access incurs a map lookup.

- ► This is a relatively heavyweight application of DBI.

- ▶ The overhead impedes interaction with the application;

- Lower interactivity means lower code coverage; and

- Limited code coverage means limited applicability.

- Furthermore, the overhead is fundamental to the approach.

- No matter how we optimize it, fundamentally, the approach instruments all memory accesses.

#### Limitations of DBI-Based Solutions

Limitation #2: Overhead from Tracking Every Allocation

- Every instrumented memory access requires a map lookup.

- ightharpoonup Binary trees ensure slow log(N) growth, but nevertheless . . .

- ... more allocations tracked means slower lookups.

- Can we reduce the overhead even further?, and/or

- Is it useful to track only a subset of allocations?

#### Limitations of DBI-Based Solutions

Friendliness as an Interactive Tool

- DBI solution is fire-and-forget, monolithic, and slow.

- ► Can we make a useful interactive reverse engineering tool?

- ▶ How best to offer the results within Hex-Rays and IDA?

- ► GUIs for browsing the results

- Full automation for common type annotation tasks

- Library elements for custom tasks

### Directions Explored in this Research

- 1. Track memory accesses via page-related chicanery.

- 2. Allow the user to specify particular allocation sites of interest, rather than targeting all at once.

- 3. Divert interesting allocations into custom allocators.

- 4. Performance-optimize everything.

- 5. Make good use of the resulting data.

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

My Contributions to this Problem

Exploit X86 Demand-Based Paging

DLL Injection-Based Memory Tracking

Target Specific Allocation Sites

Exploit the Results within IDA/Hex-Rays

Target-Specific Example: unions

#### Focus on the Memory, not the Instructions

Idea #1: Debug Breakpoints

First idea for replacing DBI: X86 debug/memory breakpoints.

```

mov rcx, 20h

call malloc  ; Set 8-byte R/W breakpoint on:

; rax+0x00

; rax+0x08

; rax+0x10

; rax+0x18

```

- PRO: only incurs overhead when the memory is accessed

- ► CON: can only set 4 breakpoints, i.e., 0x20 bytes of memory

- Would like to track megabytes/gigabytes, not "bytes".

Verdict: right direction, wrong scale.

#### Focus on the Memory, not the Instructions

Idea #2: Page Breakpoints

Second idea for replacing DBI: SoftICE's BPR feature.

```

mov rcx, 88h

call malloc SoftICE command:

:bpr rax rax+0x88 rw

```

- Unlimited memory breakpoints of any size!

- Can be implemented in kernel-mode or user-mode.

- Note, also implemented by other tools:

- ► IDA's large memory breakpoints

- OllyDbg's page breakpoints

Sounds promising! Let's review how it works.

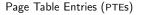

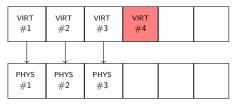

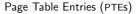

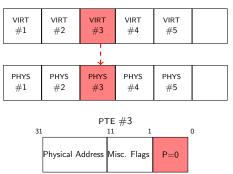

Virtual Memory Concept

The OS provides the illusion of a large virtual address space, but only mapped addresses are valid. (E.g., #4 is not.)

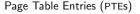

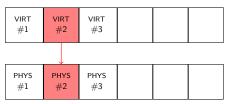

Virtual-to-Physical Address Translation

The page table maintains the virtual-to-physical mappings. E.g. if virtual 0x76543000 is mapped to physical 0x12345000, then

$$0x76543 012$$

resolves to  $0x12345 012$ .

VirtualOffset PhysicalOffset

On-Demand Growth of Virtual Address Space

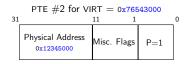

The OS can grow the virtual address space on demand by allocating and mapping additional physical pages.

Swapping Under High Memory Load

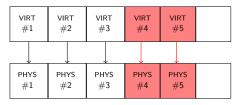

When memory is scarce, the OS reclaims physical pages by:

- 1. Writing their contents to disk.

- 2. Marking the corresponding PTE entry as non-present (P=0).

Later accesses to non-present pages generate page fault exceptions.

Transparently Reloading Swapped Pages

In response to page faults in non-present pages, the OS:

- 1. Allocates a physical page.

- 2. Loads the page's previous contents from disk.

- 3. Updates the PTE with the physical address and P=1.

- 4. Resumes execution.

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

#### My Contributions to this Problem

Exploit X86 Demand-Based Paging

DLL Injection-Based Memory Tracking

Target Specific Allocation Sites

Exploit the Results within IDA/Hex-Rays

# Memory Tracing via Presence Overview

SoftICE's BPR, IDA's large memory, and OllyDbg's page breakpoints co-opt X86's demand paging mechanism as such:

- Mark pages of interest as non-present.

- Intercept page fault exceptions for those pages.

- Determine whether the region of interest was accessed;

- Break if so, continue execution if not.

We exploit this same mechanism to track structure accesses.

Mechanism in Detail

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

Before the first instruction executes, assume that the page at [ebx+4] has been marked as non-present.

Mechanism in Detail

► 61F33E5A mov eax, [ebx+4] 61F33E60 add edx, 4

First instruction attempts to execute.

Mechanism in Detail

► 61F33E5A mov eax, [ebx+4] → EXCEPTION: Page Fault

Since [ebx+4] is non-present, the CPU triggers a page fault exception.

Mechanism in Detail

### Our Exception Handler

```

61F33E5A mov eax, [ebx+4]

Page Fault if(!ourFault())

61F33E60 add edx, 4

return;

```

The OS transfers control to our exception handler.

Mechanism in Detail

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

```

EXCEPTION:

Page Fault

```

```

Our Exception Handler

```

```

if(!ourFault())

return;

```

If the address was not within a tracked region, we pass.

Mechanism in Detail

```

► 61F33E5A mov eax, [ebx+4] EXCEPTION: Page Fault

```

```

Our Exception Handler

```

```

log(exnDetails);

save(faultEa); ◀

```

Log structure access (identically to what we did for DBI). Also, record the address of the faulting instruction (61F33E5A ◀ in this case).

Mechanism in Detail

Our Exception Handler

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

```

EXCEPTION:

Page Fault

```

makePresent(page);

Mark the page at [ebx+4] as present again.

Mechanism in Detail

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

```

EXCEPTION:

Page Fault

```

```

Our Exception Handler

```

- setTrapFlag();

- resumeExecution();

Set the X86 trap flag (TF). This will allow one instruction to execute, after which a single-step exception will be raised. Continue execution of the monitored program.

Mechanism in Detail

► 61F33E5A mov eax, [ebx+4] 61F33E60 add edx, 4

The first instruction executes again. Since the page at [ebx+4] is now present, execution succeeds this time.

Mechanism in Detail

```

61F33E5A mov eax, [ebx+4] → EXCEPTION: Single Step

```

The second instruction would execute, but since the TF was previously set, the CPU raises a single-step exception.

Mechanism in Detail

```

Our Exception Handler

61F33E5A mov eax, [ebx+4] Single Step

if(!ourFault())

return;

```

The OS invokes our single step exception handler. Ensure that the faulting address ◀ is immediately after the previously-saved faulting address ◀. If not, we pass.

Mechanism in Detail

Our Exception Handler

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

makeNonPresent(page);

Mark the page at [ebx+4] as non-present again, ensuring that we catch future accesses to the monitored page.

Mechanism in Detail

Our Exception Handler

```

61F33E5A mov eax, [ebx+4]

61F33E60 add edx, 4

```

```

EXCEPTION:

Single Step

```

resumeExecution();

Resume execution of the program.

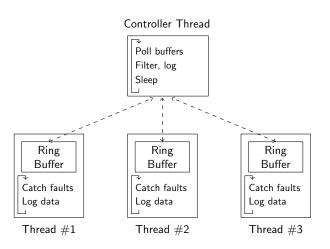

Multi-Threaded Architecture

A dedicated thread retrieves events from the program's thread-local data, filters duplicates, and logs the results to disk via buffered I/O.

# Memory Tracing via Presence Optimizations

#### Optimization ideas implemented:

- 1. Emulate common instructions instead of single-stepping<sup>1</sup>

- 2. Use guard pages instead of PAGE\_NOACCESS<sup>2</sup>

- 3. Force consumer thread away from producer thread cores

| Architectural                      | # Accesses |

|------------------------------------|------------|

| Revision                           | per Minute |

| Single-Threaded                    | 3M         |

| Multi-Threaded                     | 6.4M       |

| Mini X64 Emulator V1               | 9M         |

| Guard Pages                        | 11M        |

| <pre>SetThreadAffinityMask()</pre> | 12.1M      |

| Mini X64 Emulator V2               | 13.2M      |

<sup>&</sup>lt;sup>1</sup>Suggested by Yaron Dinkin

<sup>&</sup>lt;sup>2</sup>Suggested by Jason Geffner + RECON attendee whose name I forget (sorry)

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

#### My Contributions to this Problem

Exploit X86 Demand-Based Paging DLL Injection-Based Memory Tracking Target Specific Allocation Sites

Exploit the Results within IDA/Hex-Rays

Target-Specific Example: unions

How to Apply Page-Based Tracking

We've shown how to track memory, but not how to apply it. We explore our two possibilities, and strategies for those cases:

- 1. Track every allocation, a la DBI.

- 2. Only track certain allocations.

Tracking Every Allocation

#### When tracking all allocations:

Simply add breakpoints upon malloc, and remove upon free.

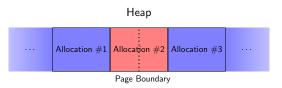

Noisiness of Technique

When tracking only some allocations:

- Since our technique works at the level of pages, we incur page faults for any allocation on the same page.

- Only interested in red region.

- ► However, we take faults in blue regions on the same page.

- ightharpoonup More page faults = more overhead.

Noisiness of Technique

When tracking only some allocations:

- Since our technique works at the level of pages, we incur page faults for any allocation on the same page.

- Only interested in red region.

- ▶ However, we take faults in blue regions on the same page.

- ► More page faults = more overhead.

- Worse, we may monitor multiple pages per allocation.

- ▶ Best performance: **only** fault on interesting allocations.

Divert into Custom Allocator

When tracking only specific allocations, to improve performance:

Divert interesting allocations into a custom allocator.

Benefit: no page faults for uninteresting allocations!

Divert into General-Purpose, Off-the-Shelf Allocator

One strategy for custom allocation: use an existing allocator.

```

HANDLE hHeap = HeapCreate(...);

//...

void *customAlloc(size) {

return HeapAlloc(hHeap,0,size);

}

```

#### Pros:

- Easy to implement

- Usually thread-safe

- Naturally handles different-sized allocations

- ► Tuned for performance

```

void customFree(void *mem) {

HeapFree(hHeap,0,mem);

}

```

#### Cons:

- Page faults for in-band metadata

- Slower than some alternatives

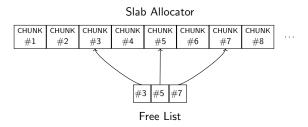

Divert into Customized Slab Allocator

Another allocation strategy: fixed-size slab allocator.

#### Pros:

- ► Fast allocation and range checks

- ► No in-band metadata

#### Cons:

- Fixed-size

- Must be applied judiciously

Summary: DBI vs. DLL Injection

### DBI

- 1. Hook malloc/free

- 2. Record allocation details

- 3. Instrument memory references

- 4. Keep accesses to allocations

- 5. Log structure accesses

- 6. Post-process data

# **DLL** Injection

- 1. Hook malloc/free

- 2. Divert chosen allocations into custom allocator

- 3. Mark allocations non-present

- 4. Catch memory exceptions

- 5. Log structure accesses

- 6. Post-process data

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

#### My Contributions to this Problem

Exploit X86 Demand-Based Paging

DLL Injection-Based Memory Tracking

Target Specific Allocation Sites

Exploit the Results within IDA/Hex-Rays

Target-Specific Example: unions

Loading the Data in IDA

Load raw structure accesses (unknown type)

Load raw structure accesses (known type)

Load raw union accesses

Import function argument data

Import allocation site types

Export allocation site types

Font...

Right-click in the main GUI window.

- ▶ **Unknown structure**: for structure recovery purposes.

- **Known structure**: when the structure type is already known.

- This case is still very useful, as we will see.

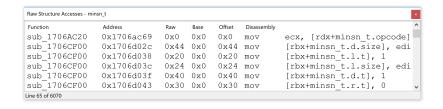

#### List of Raw Structure Accesses

| Function     | Address    | Raw  | Base | Offset | Disassembly |                     |

|--------------|------------|------|------|--------|-------------|---------------------|

| sub 170BC450 | 0x170bc452 | 0x18 | 0x0  | 0x18   | mov         | [rcx+18h], edx      |

| sub 170BC450 | 0x170bc455 | 0x8  | 0x0  | 0x8    | mov         | [rcx+8], rax        |

| sub 170BC450 | 0x170bc459 | 0x10 | 0x0  | 0x10   | mov         | [rcx+10h], rax      |

| sub 170BC450 | 0x170bc45d | 0x0  | 0x0  | 0x0    | mov         | [rcx], rax          |

| sub 1706CF00 | 0x1706cf0f | 0x0  | 0x0  | 0x0    | mov         | [rdx], r8d          |

| sub 1706CF00 | 0x1706d000 | 0x18 | 0x0  | 0x18   | mov         | r9d, [rbx+18h]      |

| sub 1706CF00 | 0x1706d00b | 0x0  | 0x0  | 0x0    | mov         | dword ptr [rbx], 4  |

| sub 17149E60 | 0x17149e8d | 0x20 | 0x20 | 0x0    | cmp         | byte ptr [rbx], 2   |

| sub 17144EB0 | 0x17144ec7 | 0x20 | 0x20 | 0x0    | movzx       | eax, byte ptr [rcx] |

After loading the access data for some allocation site(s).

#### Raw Structure Access Operations

Apply structure references to disassembly (all)

Apply structure references to disassembly (selected)

Apply types to Hex-Rays variables (all)

Apply types to Hex-Rays variables (selected)

Font...

#### Right-clicking provides two primary operations:

- 1. Apply structure offsets in the disassembly.

- 2. Change the types of variables in Hex-Rays.

Applying Structure Offsets in the Disassembly

Applying structure offsets is extremely fast.

Structure Cross-References

```

struc ; (sizeof=0x10, align=0x8, copyof 1459)

mop t

XREF: minsn t/r

minsn t/r ...

XREF: sub 17007ED0+16/w

db ?

xrefs to mop_t.t

X

+EA/r

Directic Ty Address Text

+AB/w

™Up w sub… mov

dword ptr [rcx+minsn t.l.t],

dword ptr [rcx+minsn t.r.t], 0

☑Up w sub… mov

+1D/w

dword ptr [rcx+minsn t.d.t],

☑Up w sub... mov

OK

Cancel

Search

Help

+129/r

Line 1 of 1243

; sub 1700B6D0+DA/r

ends

mop t

```

You can browse cross-references in the structures window.

1243 free structure references to that field alone!

Locating Hex-Rays Variables

```

ptr.1

ea: 1706AC8A

BYTE

add

ea: 1706AC8A

BYTE *

cast

pum 64

ea: FFFFFFFF

ea: 1706AC8A

BYTE *

var.8 v2

ea: FFFFFFFF

unsigned int

```

```

1706AC8A movzx eax, byte ptr [rbx+40h]

```

For a given discovered structure access, locate the pointer dereference at that address in the Hex-Rays CTREE.

Does not always work. Hex-Rays may:

- Lose track of the address of the memory dereference;

- Not create a variable for the pointer dereference;

- ▶ Render the access via many patterns, some of which I miss.

Can be improved somewhat, but will never be perfect.

Applying Hex-Rays Variable Types

```

v4 = (_DWORD *)qalloc_or_throw(80i64);

v5 = (__int64)v4;

if ( v4 )

{

v4[offsetof(minsn_t, next)] = 0;

v4[9] = -1;

v4[0xC] = 0;

v4[0xD] = -1;

v4[offsetof(minsn_t, prev)] = 0;

v4[0x1] = -1;

sub_170BC450((__int64)v4, -1);

}

```

```

v4 = (minsn t *) galloc or throw(80i64);

if ( v4 )

v4->1.t = 0;

v4->1.oprops = 0;

v4->1.valnum = 0:

v4->1.size = -1:

v4->r.t = 0:

v4->r.oprops = 0;

v4->r.valnum = 0;

v4->r.size = -1;

v_4 - d.t = 0;

v4->d.oprops = 0;

v4->d.valnum = 0;

v4->d.size = -1:

sub 170BC450(( int64)v4, -1);

```

Comparison before and after applying Hex-Rays types.

Existing DBI-Based Approaches Limitations of DBI-Based Solutions

#### My Contributions to this Problem

Exploit X86 Demand-Based Paging DLL Injection-Based Memory Tracking Target Specific Allocation Sites Exploit the Results within IDA/Hex-Rays

Target-Specific Example: unions

unions

```

union U {

int x;

char *y;

void *z;

};

```

- unions allow multiple interpretations of the same variable.

- ▶ U can hold either an int, x, OR a char \*, y, OR a void \*, z.

Tagged unions

- ▶ The tagged union pattern associates an enum with a union.

- **t** is called the **tag** or the **discriminant**.

- ► This design pattern is especially common in programming language tools (compilers, interpreters, decompilers, etc).

Tag Checking

```

void print(taggedU *u) {

if(u->t == Uint)    printf("%d\n", u->e.x);

if(u->t == Ucptr) printf("%s\n", u->e.y);

if(u->t == Uvptr) printf("%llx\n",u->e.z);

};

```

- ▶ The code must check the tag to know the union's held type.

- ► Code using unions is **littered** with these checks.

unions in Decompilation: Improper Selection

```

v162 = (int64) &v8->1;

v163 = v8 -> 1.nnn;

if (v163->ea - 8 <= 1)

v162 = (int64) & v163[1].value;

if ( *( BYTE *)v162 == 4

&& **( DWORD **) (v162 + offsetof(mop t, u4)) == 10

&& (v154 == (mop t **)255 || v154 == (mop t **)0xFFFF

v164 = (int)sub 61F66290((unsigned int)v154) / 8;

if ( *( DWORD *) (v162 + 4) >= v164 )

*( DWORD *) (v162 + 4) = v164;

*( DWORD *) (*( OWORD *) (v162 + 8) + 68i64) = v164;

```

Proper union field selection is critical to readable decompilation. Failure to do so leads to hideous code like this.

unions in Decompilation: Proper Selection

```

v163 = &v8->1;

v164 = v8 -> 1.d:

if ( (unsigned int) (v164->opcode - 8) <= 1)

v163 = &v164 -> 1;

if (v163->op == 4

&& v163->d->opcode == 10

&& (v155 == (mop t **) 255 || v155 == (mop t **) 0xFFFF ||

v165 = (signed int) sub 61F66290((unsigned int) v155) / 8;

if (v163->size >= v165)

v163->size = v165;

v163->d->d.size = v165;

```

Same code as the previous, with three union fields set properly. unions are particularly tedious to apply manually — let's automate.

Upon Manually Discovering a union Somewhere ...

```

class mop_t {

+0x00 mopt_t t; ◀

+0x01 char oprops;

+0x02 short valnum;

+0x04 int size;

+0x08 union { . . . }; ◀

+0x10 };

```

- ▶ Suppose we discover a tagged union within an allocated type.

- ► Suppose we discover the tag location at +0x00 <.

- Suppose we discover the union location at +0x08 ◀.

- ▶ Run the structure access discovery again, but this time:

- Only log accesses to the union region.

- ▶ Log the value of the enum at every union access. <</p>

Determine the Number of Union Variants

| RVA    | enum              | Туре |

|--------|-------------------|------|

| 150F03 | 0 <mark>x2</mark> | READ |

| 151F8A | OxA               | READ |

| 1520BC | 0xC               | READ |

| 14E9AE | 0x8               | READ |

| 15EB78 | 0 <b>x4</b>       | READ |

| 1531A8 | 0 <b>x4</b>       | READ |

| 146F01 | 0xE               | READ |

This data helps determining the number of union variants. Create a union with this many variants (of the observed sizes).

Mapping between enum Elements and union Fields

```

enum mop_t {

union {

mop_z

mreg_t r;

mop_r

= 2, ----→ 1

mnumber_t *nnn;

mop_n

minsn_t *d;

mop_str = 3, \

= 5, ---> 3

stkvar_ref_t *s;

mop_d

= 6, ----- 4

ea_t g;

mop_S

= 7, ----> 5

int b:

mop_v

= 8, ----- 6

mfuncinfo t *f:

mop_b

= 9, ---- 7

lvar ref t *1:

mop_f

= 10, ---- 8

mop_addr_t *a;

mop_1

= 11, ---- 9

char *helper;

mop_a

char *cstr:

mop_h

= 12, ----→11

mcases_t *c;

mop_c

mop_fn = 13, ---- \rightarrow 12

fnumber_t *fpc;

= 14, ----→13

mop_pair_t *pair;

mop_p

scif_t *scif;

mop_sc

};

};

```

Through reverse engineering, manually establish a mapping between the enum elements and union variant numbers.

Setting Hex-Rays Union Selections

17150D86 mov rbx, [rbx+28h]

- 1. First, set the type of the base variable, as before.

- 2. Next, locate the union reference .

- 3. Finally, apply the proper union element number, based on the tag value recorded at runtime.

Preprocessing Run-Time Data Collection Applying the Results

Overview: Big Picture

Via DLL injection, for every call to malloc, record the pointer.

```

loc_567:

v4 = malloc(0x138);

sub_123(a1,v9,0);

sub_234(v1+24,"a");

sub_345(a3,a2,v17+16);

```

Discover every function receiving an allocated pointer as argument. Record  $\langle$  function RVA, arg #, allocation RVA, size, pointer offset  $\rangle$ . E.g., record  $\left|\langle 0x345, \#3, 0x567, 0x138, 16 \right\rangle$ .

Preprocessing #1: Locate Functions via x64 Exception Directory

```

RUNTIME_FUNCTION <rva sub_61EB80C0 \blacktriangleleft, rva algn_61EB80DB \blacktriangleleft, rva stru_620C0390>

```

```

61EB80C0 sub_61EB80C0 ◀proc near

61EB80C0 var_18= qword ptr -18h

61EB80C0 sub rsp, 38h

61EB80C4 mov [rsp+38h+var_18], -2

61EB80D1 call free

61EB80D6 add rsp, 38h

61EB80DA retn

61EB80DA sub_61EB80C0 endp

61EB80DB algn_61EB80DB: align 20h ◀

```

- ► The PE64 Exception Directory has RUNTIME\_FUNCTION entries.

- ► These give the beginning of every non-leaf function <,

- ▶ and its end (or the beginning of its first try block) ◄.

Preprocessing #2: Filter Unusable Functions

```

► 61EB80C0 sub rsp, 38h

61EB80C4 mov [rsp+38h+var_18], -2

61EB80CD mov rcx, [rcx+60h]

```

Iterate through the function's instructions. FAIL if instruction:

- Cannot be decoded

- ▶ Has control-flow

- ► Is not easily relocatable

- Has incoming cross-references

- Is after function end / beginning of next try block (per X64 exception metadata)

Preprocessing #2: Filter Unusable Functions

```

61EB80C0 sub rsp, 38h

• 61EB80C4 mov [rsp+38h+var_18], -2

61EB80CD mov rcx, [rcx+60h]

```

Iterate through the function's instructions. FAIL if instruction:

- Cannot be decoded

- Has control-flow

- Is not easily relocatable

- Has incoming cross-references

- Is after function end / beginning of next try block (per X64 exception metadata)

Preprocessing #2: Filter Unusable Functions

```

61EB80C0 sub rsp, 38h

61EB80C4 mov [rsp+38h+var_18], -2

• 61EB80CD mov rcx, [rcx+60h]

```

Iterate through the function's instructions. FAIL if instruction:

- Cannot be decoded

- Has control-flow

- Is not easily relocatable

- ► Has incoming cross-references

- Is after function end / beginning of next try block (per X64 exception metadata)

Succeed after sizeof(call) bytes. ◀

Preprocessing #3: Force \_\_fastcall Calling Convention

For each kept function, get the prototype from Hex-Rays.

Remove non-\_\_fastcall-compliant arguments; reorder remaining.

Preprocessing #4: Record Positions of Pointer-Sized Arguments

```

void __fastcall

sub_61EB8AD0(

void *rcx0, ◀

unsigned int a2,

void *a3) ◀

```

For each pointer-sized argument ◀, record positions (#0, #2). (Standardized X64 \_\_fastcall makes this easier than on X86.) Discard functions with no pointer-sized arguments.

Determining argument sizes isn't perfect; Hex-Rays sometimes makes mistakes.

Preprocessing Summary

| Function RVA # | Prolog Bytes | # Args | $\# \operatorname{arg}_0$ | $\# \operatorname{arg}_1$ |  |

|----------------|--------------|--------|---------------------------|---------------------------|--|

|----------------|--------------|--------|---------------------------|---------------------------|--|

For each suitable function with pointer-size arguments, record:

- Function's location

- Number of prolog bytes

- Number, positions of pointer-sized arguments

| Function | # Prolog | # Tracked |    |      |       |     |

|----------|----------|-----------|----|------|-------|-----|

| RVA      | Bytes    | Args      | Ar | g po | ositi | ons |

| 0xe760   | 5        | 4         | 0  | 1    | 3     | 4   |

| 0x114e50 | 8        | 3         | 0  | 1    | 2     |     |

| 0xf6f60  | 5        | 3         | 0  | 1    | 3     |     |

| 0x47c20  | 6        | 2         | 0  | 1    |       |     |

| 0x10c4d0 | 5        | 2         | 0  | 1    |       |     |

Preprocessing

Run-Time Data Collection

Applying the Results

Step #1: Hook Memory Management Functions

Hook allocators via DLL injection.

As before, record allocation records from malloc until free.

#### Allocation Record

|  | Allocated pointer | Size | RVA of return address from malloc |  |

|--|-------------------|------|-----------------------------------|--|

|--|-------------------|------|-----------------------------------|--|

#### Step #2: Hook Every Suitable Function

```

.text:61F6ABD0 mov

r8, rcx

text:61F6ABD3 push

rbx

text:61F6ABD4 sub rsp, 80h

text:61F6ABDB mov [r11-68h], -2

text:6205CC10 push rdi

text:6205CC12 sub

rsp, 40h

text:6205CC16 mov [rsp+48h+var_28], -2

▶ .text:6205F91C sub rsp, 18h

.text:6205F920 mov r8, rcx

.text:6205F923 mov eax, 5A4Dh

text:61F79570 mov

rax, rsp

text:61F79573 push r14

text:61F79575 sub rsp, 60h

text:61F00AA0 sub rsp, 38h

text:61F00AA4 mov [rsp+38h+var_18], -2

▶ .text:61F00AAD mov rcx, [rcx]

```

For each function to hook ...

Step #2: Hook Every Suitable Function

```

.text:61F6ABD0

r8, rcx

text:12345600

mov

r8, rcx

COPY

.text:61F6ABD3

push

rbx

.text:12345603

push

rbx

rsp, 80h

.text:61F6ABD4

.text:12345604

sub

rsp, 80h

[r11-68h], -2

.text:61F6ABDB

.text:1234560B

jmp

COPY

.text:12345620

.text:6205CC10

push

rdi

push

rdi

.text:6205CC12

sub

rsp, 40h

.text:12345622

sub

rsp, 40h

[rsp+48h+var_28], -2

.text:6205CC16

mov

.text:12345626

COPY

.text:6205F91C

rsp, 18h

.text:12345640

rsp, 18h

.text:6205F920

r8, rcx

.text:12345644

r8, rcx

eax, 5A4Dh

.text:6205F923

.text:12345647

61F79573

COPY

.text:61F79570

.text:12345660

rax, rsp

.text:61F79573

push

.text:12345663

push

r14

.text:61F79575

rsp. 60h

.text:12345666

imp

61F79575

.text:61F00AA0 sub rsp. 38h

COPY

.text:12345680

sub

rsp. 38h

[rsp+38h+var_18].

[rsp+38h+var_18], -2

.text:61F00AA4 mov

.text:61F00AAD mov rcx. [rcx]

.text:1234568D

imp

61F00AAD

```

Allocate memory for re-entry thunks. Copy the leading instructions, and insert a jump to after the copied instructions. Record { Original RVA, Thunk VA } in a hash table.

#### Step #2: Hook Every Suitable Function

Divert every function into a common logging routine.

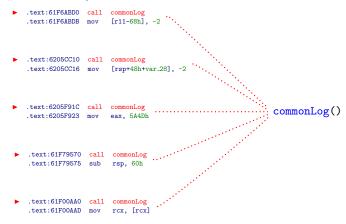

Redirect Functions into a Common Logging Stub

- commonLog just invokes its C counterpart.

Argument Logging Details

```

uint64_t commonLogC(uint64_t *args) {

funcRVA = _ReturnAddress();

#1    reEntry, argList = lookup(funcRVA);

#2    for(argNo : argList)

#2    log(funcRVA,argNo,args[argNo]);

#3    return reEntry;

}

```

- 1. Fetch re-entry address, list of interesting arguments.

- 2. Log each interesting argument.

- ► This happens in another thread for efficiency.

- 3. Return to re-entry thunk.

Filter, Log Allocation Flow to Arguments

```

void log(uint64_t funcRVA, int argNo, uint64_t arg) {

#1    allocRec = allocMapLookup(arg);

#2    if(!allocRec) return;

#3    write(funcRVA,argNo,allocRec);

}

```

- 1. Look up function argument in allocation map.

- 2. Return if not part of an allocation.

- 3. Write log entry otherwise.

#### Logged Data

| Function RVA | # Arg | Alloc RVA | Alloc size | Offset into alloc |

|--------------|-------|-----------|------------|-------------------|

|--------------|-------|-----------|------------|-------------------|

Summary: Logged Data

Logged Data

| Function RVA | # Arg | Alloc RVA | Alloc size | Offset into alloc |

|--------------|-------|-----------|------------|-------------------|

| 0x15f520     | 1     | 0xbe648   | 0x50       | 0x20              |

| 0x153ce0     | 0     | 0xbe648   | 0x50       | 0x0               |

| 0x147520     | 0     | 0x143fd8  | 0x50       | 0x40              |

| 0x15f8d0     | 1     | 0x143fd8  | 0x50       | 0x40              |

| 0x11530      | 0     | 0x56c89   | 0x630      | 0x0               |

| 0x55a80      | 0     | 0x56149   | 0x120      | 0x0               |

| 0x57bd0      | 0     | 0x56149   | 0x120      | 0x18              |

This generates a **lot** of data (~60K entries for my target).

Preprocessing

Run-Time Data Collection

Applying the Results

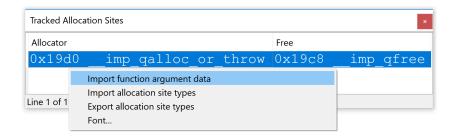

Loading the Data in IDA

- First, create an allocator/free pair.

- Can add multiple allocators if appropriate.

- Next, load the data for that allocator.

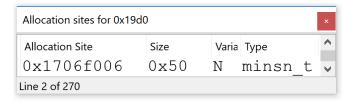

Displaying Allocation Sites and Types

| Allocation sites for 0x19d0 |      |            |          |

|-----------------------------|------|------------|----------|

| Allocation Site             | Size | Varia Type | ^        |

| 0x1707a5fc                  | 0x30 | N          |          |

| 0x170ad600                  | 0x8  | Y          |          |

| 0x17150002                  | 0x10 | N          |          |

| 0x170e9803                  | 0x10 | N          |          |

| 0x17048e04                  | 0x70 | N          |          |

| 0x1706f006                  | 0x50 | N          |          |

| 0x1714f407                  | 0x50 | N          | <b>~</b> |

| Line 1 of 270               |      |            |          |

- Double-click an allocator to see the list of data:

- 1. The address of all observed allocation sites

- 2. The size allocated by that site

- ▶ If multiple sizes, show the GCD

- 3. The user-supplied type for that site, if any

Displaying Allocation Site Flow Data

| Allocation flow for 0x1707a5fc[0x30] |       |        |      |   |  |

|--------------------------------------|-------|--------|------|---|--|

| Function                             | Arg # | Offset | Size | ^ |  |

| sub_170735A0                         | 1     | 0x0    | 0x30 |   |  |

| sub_17165AA0                         | 1     | 0x0    | 0x30 |   |  |

| sub_17048840                         | 0     | 0x0    | 0x30 |   |  |

| sub 1704D5F0                         | 3     | 0x0    | 0x30 |   |  |

| sub 170DCC30                         | 1     | 0x0    | 0x30 |   |  |

| sub_17111040                         | 0     | 0x0    | 0x30 |   |  |

| sub 1713BCD0                         | 1     | 0x0    | 0x30 | ~ |  |

| Line 1 of 155                        |       |        |      |   |  |

- Double-click an allocation site to see the list of:

- 1. Functions and arguments into which the allocations flowed

- 2. Observed offsets from the base of the allocation

Displaying Allocation Flow in Hex-Rays

```

Pseudocode-A

1// Dynamic allocation flow data

2// 0

3// 0x1717b823[0x138]

4// 0x17181421[0x138]

5// 0x17180fb1[0x138]

6// 1

7//

0x1717b823[0x138]+216

8// 0x17180fb1[0x138]+88

9// 0x17181421[0x138]+88

10// 0x1717b823[0x138]+88

11// 0x1717b823[0x138]+152

12// 0x17181421[0x138]+152

13// 0x17181421[0x138]+216

14// 0x17180fb1[0x138]+216

15// 0x17180fb1[0x138]+152

16 int64 fastcall sub 171173C0( int64 a1, int64 a2, int a3)

```

Hex-Rays listings will automatically display allocation flow data.

Setting Allocation Site Types

```

v10 = (_DWORD *) qalloc or throw(80i64);

if ( v10 ) Set call type...

```

Once known, the user manually sets the allocation site type.

```

(Or, in IDA: Edit->Operand Type->Set Operand Type)

```

After refresh, the allocation sites window shows the type.

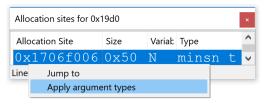

#### Applying Argument Types

For known allocation site types, the user can apply argument types.

Can select multiple allocation sites at once.

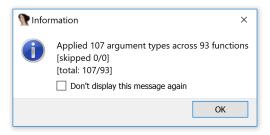

Applied Argument Types

```

char __fastcall sub_17193950(__int64 a1, minsn_t *a2, mop_t *a3, mop_t *a4, mop_t *a5)

```

Way better than doing it by hand, isn't it?

Related Types

| Offset | Type Name |       | Func EA      | Ara # | Alloc RVA  | Alloc Offset | Size  | , |

|--------|-----------|-------|--------------|-------|------------|--------------|-------|---|

| 0x0    | mblock t  |       | 0x17141040   |       | 0x170bcac4 |              | 0x178 |   |

| 0x98   | bitset t  |       | 0x1700cf00   | 0     | 0x170bcac4 | 0x98         | 0x178 |   |

| 0x70   | bitset t  |       | 0x170112e0   | 0     | 0x170bcac4 | 0x70         | 0x178 |   |

| 0x70   | bitset t  |       | 0x170112e0   | 0     | 0x170bcac4 | 0xc0         | 0x178 |   |

| 0xc0   | bitset t  |       | 0x170112e0   | 0     | 0x170bcac4 | 0x70         | 0x178 |   |

| 0xc0   | bitset t  |       | 0x170112e0   | 0     | 0x170bcac4 | 0xc0         | 0x178 |   |

| 0xe8   | unsigned  | int64 | * 0x170112e0 | 1     | 0x170bcac4 | 0xe8         | 0x178 |   |

For a given allocation site, for each offset passed to a function argument, display the types of other structure fields passed to the same argument.

## Further Extensions and Challenges

Extensions Challenges

#### Combination with Static Analysis

Access data only covers observed behaviors. E.g., will not discover the accesses ◀ below.

```

Rename Ivar... N

Set Ivar type... Y

Convert to struct *...

Create new struct type...

```

Can use Hex-Rays struct analysis to discover other accesses ◀.

# Further Extensions Writes-Pointer-To Tracking

When writing a pointer-sized value into a tracked allocation:

```

.text:170B3AD6 mov [rax+8], rdx ◀

```

If rdx points within a known allocation, log the details. This can help determining the pointer types of structure fields.

Maximum Size of Pointed-To Objects

Want to know: how big is the thing an argument points to?

| Offset | Size | Max  |

|--------|------|------|

| 0x00   | 0x30 | 0x30 |

| 0x40   | 0x50 | 0x10 |

| 0x2C   | 0x30 | 0x04 |

Example data reaching a function argument

- Maximum size is the distance from the offset to the end.

- ► Take the minimum across all data points.

Inheritance Discovery by Access Location

Derived classes must construct base classes first:

GraceWireGeneric \* thiscall GraceWireGeneric Constructor(

```

O042CFF0 GraceWireGeneric_Constructor proc near

...

0042D020 push 4

0042D025 call GraceObject_Constructor

```

Inheritance Discovery by Access Location

```

GraceObject *_thiscall GraceObject_Constructor(

{

this->iVarietyEnum = aVariety;

this->vtbl = &GraceObject::'vftable';

00424096 mov [edi+8], eax

00424099 lea eax, [edi+0Ch]

0042409C push eax

0042409D mov [ebp+a5], eax

004240A0 mov dword ptr [edi], offset vtbl

```

- ► Hence, every class in a single-inheritance hierarchy should have the same address for its first access.

- ► CAVEAT: inlined constructors will break this.

### Further Extensions and Challenges

Extensions

Challenges

# Challenges Code Coverage

As with any dynamic analysis, results limited to covered code.

```

if(v1 != 0) { // ALWAYS OBSERVED TAKEN

x->f0 = 1234;

x->fC = 0;

} else { // NEVER OBSERVED TAKEN

neverExecutedFunc1(x);

neverExecutedFunc2(x);

}

```

I offer no real contributions here, other than that the performance optimizations hereinbefore can increase observations per time unit.

Type-Related Ambiguity

Suppose multiple allocation sites/sizes flow to an argument.

```

class x {

int a; ◀

int b; ◀

};

```

```

+0 int a; ◀

+4 int b; ◀

+8 int c; ◀

+12 int d; ◀

```

```

class y :

public x {

int c;

int d;

};

```

What "type" should we assign the argument?

Need inheritance/composition relationships to fully resolve.

The data is still useful without knowing that, though.

Type- and Size-Related Ambiguity

Suppose multiple allocation sites/sizes flow to an argument.

```

class x {

int a;

int b;

class y :

class z :

public x {

public x {

void *d;

};

};

};

```

For derived objects, same size does not imply same type.

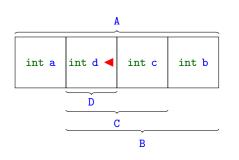

#### **Nested Structures**

```

struct A {

int a;

struct B {

struct C {

struct D {

int d;

} D;

int c;

} C;

int b;

} B;

};

```

```

int a int d int c int b

D

C

B

```

An example of nested structures.

#### Access to Nested Structure Fields

| Туре       | Expression |

|------------|------------|

| int *      | *x         |

| D *        | x->d       |

| <b>C</b> * | x->D.d     |

| B *        | x->C.D.d   |

|            |            |

- ▶ What is the C-level type of x and the accessing expression?

- ► The four possibilities are shown at right.

- ► Even if we had the structure types and nesting relationships from the source code, how would we know the type of x?

Introduction

Dynamic Structure Reconstruction

Dynamic Resolution of Argument Types

Further Extensions and Challenges

Conclusion

#### Conclusion

- None of these techniques are particularly sophisticated.

- ► However, they are easy-to-use and produce very useful results.

- Despite challenges and open problems, the results are useful.

- ▶ Automation was a better use of my RE time than reading code.

- Code needs cleanup, but will be released soon.

- Check Twitter, Reverse Engineering reddit, etc.

# Any Questions?